In the design of RISC-V FPGA, the core framework modules of RISC-V are composed.

Related reference articles:

RISC-V teaching plan

The structure of the cpu core design framework in RISC-V:  in: fii_cpu_sys.v : Project top-level module fii_iobuf.v : GPIO port logic block SYS_DCM : PLL clock module IP fii_riscv_cpu.v : RISC -V CPU module top level

in: fii_cpu_sys.v : Project top-level module fii_iobuf.v : GPIO port logic block SYS_DCM : PLL clock module IP fii_riscv_cpu.v : RISC -V CPU module top level

fii_rv32i_core.v : state machine logic module (RISC-V) running module

TDP_RAM_INSTR : Program Memory Unit (ITCM)

rv32I_exu.v : RISC -V cpu kernel module

regfile_l.v : 32 general purpose register modules

instr_dec.v : instruction decoding module

exu_alu.v : Execution module

exu_LSU.v : Load/Store module

fii_UART.v : UART module

fii_timer_lsu.v : Timer module

fii_GPIO.v : GPIO module

D_sram.v : SRAM DTCM block

exu_BRANCH.v : branch processing module

exu_csr.v : CSR register module

In the vivado project file:

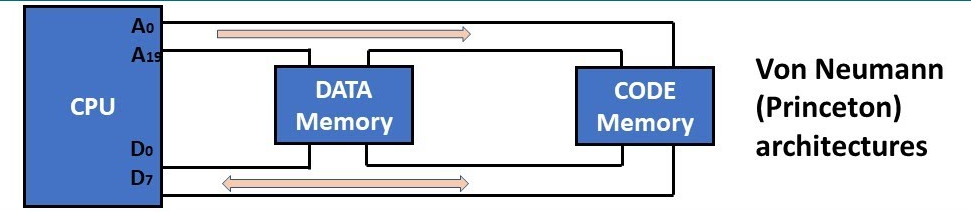

The core modules of RISC-V consist of regime_l: 32 general-purpose registers instr_dec: instruction decoding module exu_alu: Execution module exu_LSU: load/store peripheral access module exu_branch: Conditional branch module exu_CSR: CSR register module CPU architecture classification: Von Neumann Architecture: Also known as the Princeton Architecture. Its structural characteristics are that the data memory and program memory are addressed according to a unified address, such as a 32-bit address bus, which can address a 4G address space. Program memory, data memory, and peripherals each occupy a part of the 4G space and do not overlap each other.

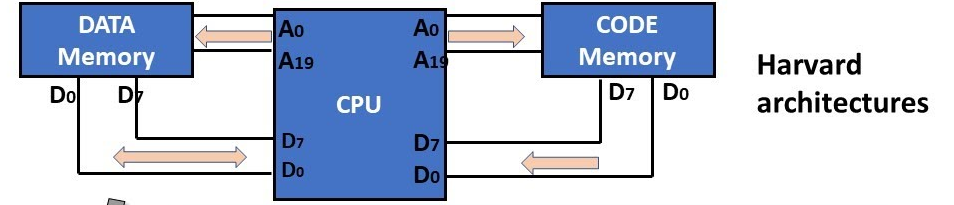

Harvard architecture: The Harvard architecture is different from the von Neumann architecture, which divides the access space linearly, but divides the data memory and the program memory into two independent addressing spaces, and maintains its own address space. The most typical structure is Intel’s earliest 8051, the 16-bit address bus can access 64k space, but with the assistance of the controller, data and programs are separated from data access and program access, so the access space is doubled

Advantages and disadvantages of von Neumann structure and Havard structure:

Von Neumann structure :

Advantages: The entire access space is linear, the entire space is coded uniformly, and the same program counter PC is used, so the requirements for the controller are relatively low, and the hardware resource (RTL) overhead is smaller than the Harvard structure.

Disadvantages: The spatial range cannot be expanded, and at the same time, due to the use of a unified spatial encoding, when a resource conflict is encountered, the program must wait for the conflict to be resolved before continuing to run the program, so the efficiency is low.

Harvard structure :

Advantages: Due to the separation of data space and program space, the entire access space is almost doubled at a time, and there is no conflict between program space access and data space access

Disadvantages: The controller is complex, two sets of PC counters are required, and the hardware overhead is high

In the current CPU design, it is not as clear-cut as in the early CPU design. It is possible that a CPU supports both the Princeton architecture and the Harvard architecture. Depending on the program and data, the CPU can read or write data from different areas. FII-RISC-V architecture: The current version of FII-RISCV v2.01 supports both the Princeton architecture and the Harvard architecture. Of course, the Harvard architecture is still relatively efficient in execution, and most applications use the Harvard architecture. But in order to show the structure of the Princeton architecture, JTAG modules will be supported in later versions, and the JTAG modules also use the Princeton architecture, this way.