In the learning of RISC-V, we provide a method to download the code written by the software personnel to the FPGA development board through the UART port, so that the user can quickly write the software program and verify the software without having to go to the FPGA every time. Comprehensive FPGA, the configuration FPGA can be verified. Greatly facilitate the development of software personnel. This function is somewhat similar to the program download of JTAG.

Related reference articles:

RISC-V teaching plan

Software Engineering Package:

asm_compile package download :

In our tutorial on learning RISC-V, we will give you a software engineering package. (asm_compile directory, the specific directory is subject to the currently downloaded version):

Create a self-built project:

This project includes some existing demo projects and gcc compiled software. There are many directories under the asm_compile directory, and each directory can be considered as a separate project. If the user wants to create his own project, he only needs to create his own directory in the asm_compile directory, and the self-built directory is also the name of the self-built project.

Create a src directory in the my_project directory, put the .s .c files written by the user in the src directory, (note: there can still be other subdirectories of source files in the src directory), if there is a header file, it will be under my_project Create the inc directory; it is not necessary to create this directory if no header files are required. Note: The names of the two directories src and inc must be fixed and should not be changed to other names.

Add self-built files to the corresponding directory. If you need header files, you need to create an inc directory

At this point, the project file is successfully created. If the user needs to add other .s .c files, they can be directly placed in the src directory; if the header file needs to be added again, just add it to the inc directory.

It is best to organize executable files. The required connection file is the sys.lds file in the asm_compile directory. This file is applicable to all current projects (this file is related to FPGA-related hardware resources, such as ITCM’s size (ROM), size of DTCM(ram))

Project compilation:

Win + R key combination, enter cmd to open the command line window, enter the directory where asm_compile is located

Run run my_project (run + project name)

If fii_asm.exe convert OK. appears, that the whole project is compiled successfully, if not, you can check the error message in the command line. The run command + project name will automatically check the .s .c .h files in the project directory, compile and link the files in the project, and finally output the relevant executable files for FPGA developers to use. Including coe, sim, mif, bin files, etc. At the same time, you can also view the relevant disassembly files to check the software-related errors.

Check out the makefile:

In the my_project directory, the obj directory will be generated, and this directory includes all the obj files generated by the files that need to be compiled in the project.

In the my_project directory, fii.bin , fii.coe, fii.map, fii.mif, fii.sim, fii.txt files will be generated. Among them:

fii.bin : Project executable (binary). This file can be downloaded to the FPGA development board using the uart tool software and run automatically.

fii.coe : This file can be used in the Vivado project, put it into the ITCM memory, and in the synthesized FPGA project, as long as it is powered on, it can run directly. It is equivalent to burning the software to the FPGA.

fii.mif : This file can be used in the Quartus project, put it in ITCM memory, and in the synthesized FPGA project, it can run directly after power on. It is equivalent to burning the software to the FPGA.

fii.map : View the location of various functions and variables in the software.

fii.sim : used for Vivado simulation, vivado can directly call this file, in the vivado project, directly simulate the project just written by the software, please refer to Loading the coe file in the Vivado simulation project

fii.txt : for viewing disassembly files. If run my_project is used, the 32 general-purpose registers in the disassembly file are x0 – x31;

If the command used is run my_project abi , the disassembly will form a file in abi format:

The contents of my_project.* and fii.* are the same. At the same time, a copy of fii.* is copied and placed in the asm_compile directory for easy download and use.

FPGA load software project :

- First, FPGA downloads the RISC-V FPGA project. (Let RISC-V CPU run).

- Press the “OK” button to pause the RISC-V CPU work, (ready to download, here is the prx100t development board as an example for reference: FII-PRX100-D (ARTIX 100T, XC7A100T) Hardware Reference Guide )

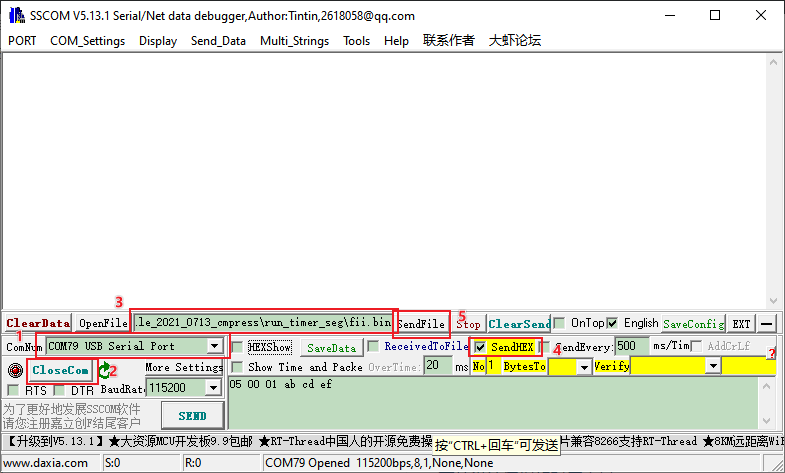

3. Through the UART software, select the my_project.bin file and send the hex file. At this time, the software can run on the FPGA development board.

Finally, click to send the file, so that the project (my_projcet) written by the software is successfully downloaded to the FPGA.