In the design of RISC-V FPGA, the core core module of RISC-V includes the instruction decoding module. The main function of this module is to…

In the RISC-V RV32I CPU core, 32 general purpose registers are required. These registers are a critical part of parsing riscv assembly instructions. Related reference…

In the design of RISC-V FPGA, the core framework modules of RISC-V are composed. Related reference articles: RISC-V teaching plan The structure of the…

Classic five-stage pipeline, RISC-V five-stage pipeline In CPU design, pipeline design is often used. Compared with the early state machine logic, pipeline design can effectively…

1.CSR register Related reference articles: RISC-V teaching plan The previous article RISC-V CSR register (1) CSR introduction and CSR instructions briefly introduced the…

1.Introduction to CSR Related reference articles: RISC-V teaching plan In addition to the 32 general-purpose registers introduced earlier, there is also a class…

1. RESET the result before generating the *.bit file First, open the Vivado FII_RISCV_V2.01 project (here, the V2.01 version is used as an example), as…

1. Introduction to assembly language format Related reference articles: RISC-V teaching plan Take asm_run_seg.S as an example: .equ BYTE_DELAY, 0x00100000 .equ GPIO_ADDR, 0xf0000000…

Related reference articles: RISC-V teaching plan Assembly language compiler environment build: After writing the assembler, you can compile it with as.exe to generate the x.bin…

Use RISC-V assembly language to write a led marquee experiment Related reference articles: RISC-V teaching plan # ASSEMBLY PROGRAM DESIGN li x8, 0xf0000000; # set…

RISCV assembly language programming (1) Marquee design This article mainly introduces the design requirements of the marquee program in assembly language programming, the concept of…

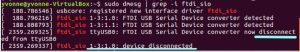

In the learning of RISC-V, we provide a method to download the code written by the software personnel to the FPGA development board through the…

1. Instruction address alignment Related reference articles: RISC-V teaching plan For load/store instructions, the address of the data in memory should be aligned.…

1. Load-Store Instructions Related reference articles: RISC-V teaching plan RV32I is a load-store architecture. Also, only load and store instructions can access memory…

1. Control transfer instruction Related reference articles: RISC-V teaching plan There are two main types of control transfer instructions in RV32I: unconditional jumps…

1. R-Type integer register-register instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (3) I-Type shift instruction and U-type…

1. I-Type shift instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (2) I-Type integer register-immediate instruction introduces 6…

1. I-type integer register-immediate instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (1) General-purpose registers and assembly instructions…

1. RISC-V general registers and program counter Related reference articles: RISC-V teaching plan This article will begin to explain the RISC-V instruction set…

1. Instruction set encoding Related reference articles: RISC-V teaching plan This article will follow the introduction of RISC-V (2) The characteristics and classification…

1. The prospect of RISC-V processors Related reference articles: RISC-V teaching plan In the last article Introduction to RISC-V (2) Characteristics and classification…

1. RISC-V instruction set features Related reference articles: RISC-V teaching plan The last article Introduction to RISC-V (1) Origin of RISC-V Describes the…

1. Instruction set architecture Related reference articles: RISC-V teaching plan Instruction Set Architecture (Instruction Set Architecture, ISA) is an abstract model that includes…

FII_RISCV_V2.01.002 version details are as follows: For FII-PRX100-D development board, JTAG model FT2232H The implementation of RISC-V CPU includes CSR, state machine core, in addition…

In python, there is often a need to modify a string in different ways. Instead of reassigning these values, we can use pre-existing methods for…

In python, there are exception cases where there empty conditionals are needed or breaking out of a while loop forcefully. The following article will explain…

Programmers often need to perform specific operations multiple times. For this, there are two types of loops for performing an operation multiple times. They are…

Conditionals are absolutely necessary for any computer programming. Conditionals perform calculations depending on whether a condition evaluates True or False. However, else and elif extend…

The main difference between dictionaries and lists or tuples is the indexes. While tuples and lists use only predetermined integer indexes, dictionaries can have custom…

In python, tuples and lists are variables that store multiple items and values. The main difference between tuples and lists is that lists are mutable…

In the world of computer science, operators are symbols that represent and perform a specific computational command. There are different operator types, and they each…

What is a variable? In computer science, variables represent memory locations, which store their own values. Variables are used to contain information and are essential…

Being able to produce an output is one of the most fundamental and important skills any aspiring programmer needs to learn. Why do we need…

After installing your IDE, it’s time to finally create your first python program. *This tutorial utilizes the PyCharm IDE. If you have not installed it…

While editing a python program, editors enjoy the luxury of being able to edit and run code on applications that support numerous different features. Rather…

Why Python? Python is a multi-paradigm programming language made by Guido Rossum in 1989, with an emphasis on code readability. It is currently the most…

Download the libjtag_hw_mbftdi-blaster.so file, which is attached at the end. Move the file to the ~/altera_lite/20.0/quartus/linux64 folder (20.0 means the Quartus version, modify it…

FII mainly uses Coremark and Dhrystone Benchmarks to evaluate the RISC-V3.01 CPU (Central Processing Units) performance on FII-PRX100-D(ARTIX-7, XC7A100T) XILINX FPGA Board (https://fpgamarketing.com/FII-PRX100-S-ARTIX-100T-XC7A100T-Xilinx-RISC-V-FPGA-Board-FII-PRX100-S-1.htm). Coremark has…

In computing, benchmarks are used to quantitatively measure the performance of the CPU. They are specially designed programs to run several iterations which includes specific…

1.Introduction Coremark has been EEMBC’s CPU evaluation standard since 2009. EEMBC (Embedded Microprocessor Benchmark Consortium) is a non-profit organization with members including Huawei, Intel, ARM and…

This article talks about how to write a executable application for the device tree driver that was just written. For related subjects, please refer to…

This article talks about how to use the echo command in user space to implement GPIO for a device tree driver. For related subjects, please…

This article breaks down and explains the device tree driver code. For related subjects, please refer to the SOC Table of Contents. First, we…

This article talks about how to write a device tree driver as well as adding the FPGA register. For related subjects, please refer to the…

This article talks about how to write a application to go with the simple character device driver that we just wrote. For related subjects, please…