Related reference articles: RISC-V teaching plan Assembly language compiler environment build: After writing the assembler, you can compile it with as.exe to generate the x.bin…

Use RISC-V assembly language to write a led marquee experiment Related reference articles: RISC-V teaching plan # ASSEMBLY PROGRAM DESIGN li x8, 0xf0000000; # set…

RISCV assembly language programming (1) Marquee design This article mainly introduces the design requirements of the marquee program in assembly language programming, the concept of…

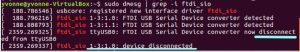

In the learning of RISC-V, we provide a method to download the code written by the software personnel to the FPGA development board through the…

1. Instruction address alignment Related reference articles: RISC-V teaching plan For load/store instructions, the address of the data in memory should be aligned.…

1. Load-Store Instructions Related reference articles: RISC-V teaching plan RV32I is a load-store architecture. Also, only load and store instructions can access memory…

1. Control transfer instruction Related reference articles: RISC-V teaching plan There are two main types of control transfer instructions in RV32I: unconditional jumps…

1. R-Type integer register-register instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (3) I-Type shift instruction and U-type…

1. I-Type shift instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (2) I-Type integer register-immediate instruction introduces 6…

1. I-type integer register-immediate instruction Related reference articles: RISC-V teaching plan The above RISC-V instruction set explanation (1) General-purpose registers and assembly instructions…

1. RISC-V general registers and program counter Related reference articles: RISC-V teaching plan This article will begin to explain the RISC-V instruction set…

1. Instruction set encoding Related reference articles: RISC-V teaching plan This article will follow the introduction of RISC-V (2) The characteristics and classification…

1. The prospect of RISC-V processors Related reference articles: RISC-V teaching plan In the last article Introduction to RISC-V (2) Characteristics and classification…

1. RISC-V instruction set features Related reference articles: RISC-V teaching plan The last article Introduction to RISC-V (1) Origin of RISC-V Describes the…

1. Instruction set architecture Related reference articles: RISC-V teaching plan Instruction Set Architecture (Instruction Set Architecture, ISA) is an abstract model that includes…

FII_RISCV_V2.01.002 version details are as follows: For FII-PRX100-D development board, JTAG model FT2232H The implementation of RISC-V CPU includes CSR, state machine core, in addition…

Download the libjtag_hw_mbftdi-blaster.so file, which is attached at the end. Move the file to the ~/altera_lite/20.0/quartus/linux64 folder (20.0 means the Quartus version, modify it…

FII mainly uses Coremark and Dhrystone Benchmarks to evaluate the RISC-V3.01 CPU (Central Processing Units) performance on FII-PRX100-D(ARTIX-7, XC7A100T) XILINX FPGA Board (https://fpgamarketing.com/FII-PRX100-S-ARTIX-100T-XC7A100T-Xilinx-RISC-V-FPGA-Board-FII-PRX100-S-1.htm). Coremark has…

In computing, benchmarks are used to quantitatively measure the performance of the CPU. They are specially designed programs to run several iterations which includes specific…

1.Introduction Coremark has been EEMBC’s CPU evaluation standard since 2009. EEMBC (Embedded Microprocessor Benchmark Consortium) is a non-profit organization with members including Huawei, Intel, ARM and…

Reference materials: RISC-V User-Level ISA RISC-V Privileged Architecture RISC-V Address Map version FII-PRX100-D schematics SiFive Freedom Studio Manual FII-PRX100-D(ARTIX 100T,XC7A100T) Hardware Reference Guide FII RISC-V…